# **UD** info Corp.

**PCMCIA ATA Flash Card**

**Product Specification**

Version 1.2

© 2023 UD INFO Corp. All right reserved. Specifications are subject to change without prior notice.

#### UD info CORP.

3F-4, No.8, Ln. 609, Sec. 5, Chongxin Rd., Sanchong Dist., New Taipei City 241, Taiwan (R.O.C.)

TEL: +886-2-7713-6050 FAX: +886-2-8511-3151

E-mail: sales@UDinfo.com.tw

# **Contents:**

| 1.  | Scope  | e          |                                                         | 2   |

|-----|--------|------------|---------------------------------------------------------|-----|

| 2.  | Intro  | duction    |                                                         | 2   |

| 3.  | Syste  | m Featur   | es                                                      | 3   |

| 4.  | Produ  | ıct Specif | fications                                               | 4   |

|     | 4.1.   | Systen     | n Environmental Specification                           | 4   |

|     | 4.2.   | Systen     | n Power Requirement                                     | 4   |

|     | 4.3.   | Systen     | n Performance                                           | 5   |

|     | 4.4.   | Systen     | n Reliability                                           | 5   |

|     | 4.5.   | Physic     | al Characteristics                                      | 6   |

|     |        | 4.5.1.     | Physical Specifications                                 | 6   |

|     |        | 4.5.2.     | PCMCIA-ATA Flash Card Dimension                         | 6   |

|     | 4.6.   |            | ity Specification                                       |     |

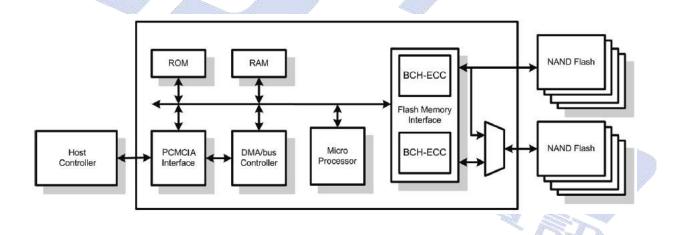

|     | 4.7.   | Card B     | lock Diagram                                            | 7   |

| 5.  | Interf | ace Desc   | ription                                                 | 8   |

| 100 | 5.1.   |            | signments                                               |     |

|     | 5.2.   |            | scriptions                                              |     |

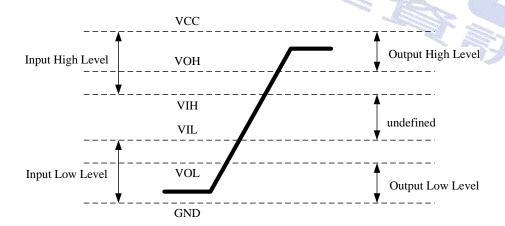

| 7.  | Electr | ical Spec  | ification                                               | 16  |

|     | 7.1.   |            | Pin Description                                         |     |

|     | 6.1.   | Absolu     | ute Maximum Rating                                      |     |

|     |        | 6.1.1.     | PCMCIA-ATA FLASH CARD interface I/O at 5.0V             |     |

|     |        | 6.1.2.     | PCMCIA-ATA FLASH CARD interface I/O at 3.3V             | 17  |

|     |        | 6.1.3.     | The I/O pins other than PCMCIA-ATA FLASH CARD interface |     |

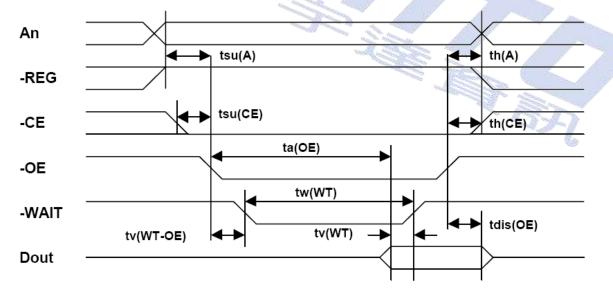

|     | 6.2.   |            | nmended Operating Conditions                            |     |

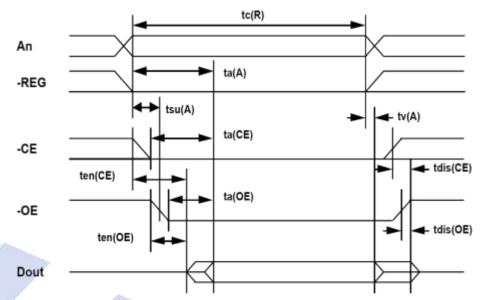

|     | 6.3.   | AC Cha     | aracteristics                                           | 100 |

|     |        | 6.3.1.     | Attribute Memory Read Timing                            | 18  |

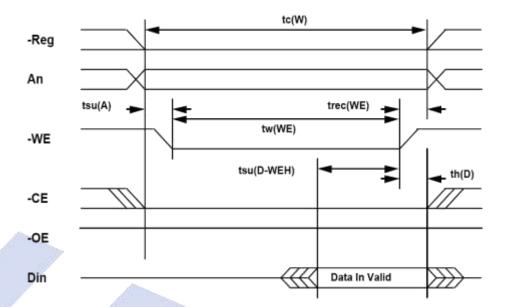

|     |        | 6.3.2.     | Configuration Register (Attribute Memory) Write Timing  | 19  |

|     |        | 6.3.3.     | Common Memory Read Timing                               | 21  |

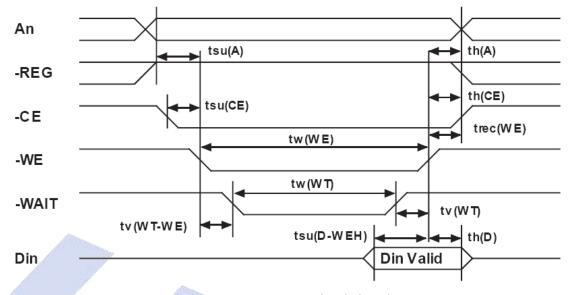

|     |        | 6.3.4.     | Common Memory Write Timing                              | 22  |

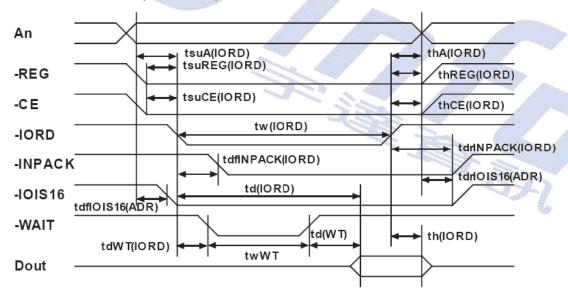

|     |        | 6.3.5.     | I/O Read Timing                                         | 24  |

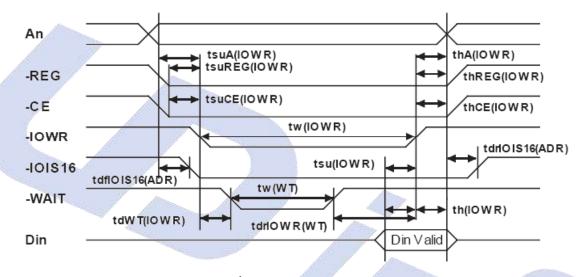

|     |        | 6.3.6.     | I/O Write Timing                                        | 26  |

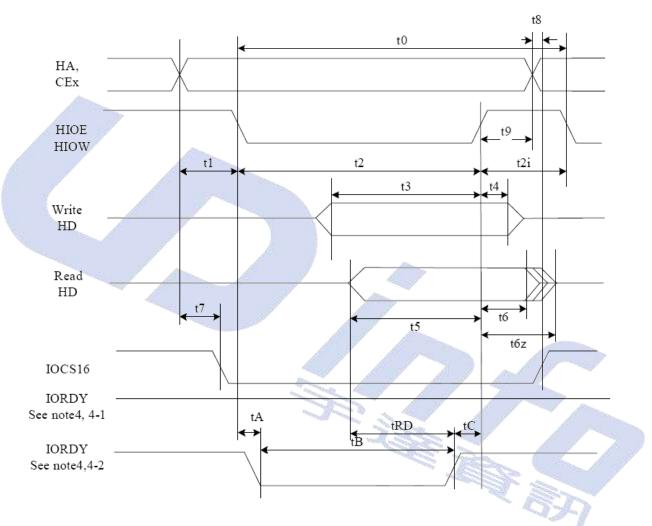

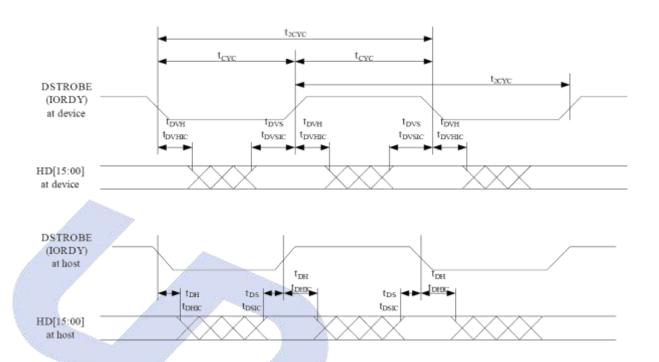

|     |        | 6.3.7.     | True IDE PIO Mode Read/Write Timing                     | 28  |

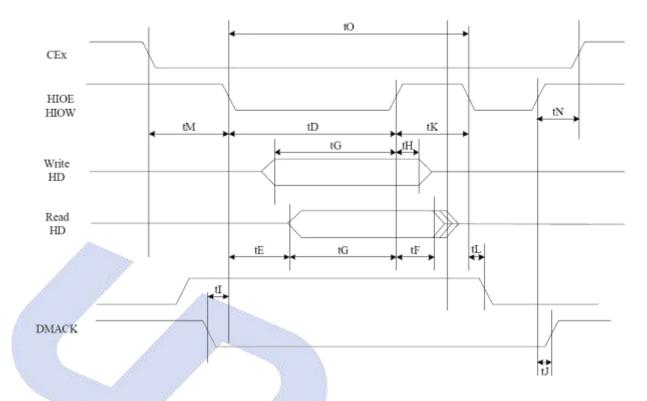

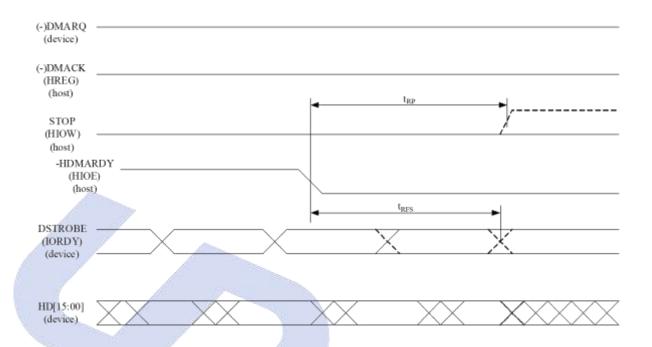

|     |        | 6.3.8.     | True IDE Multiword DMA Mode Read/Write Timing           | 31  |

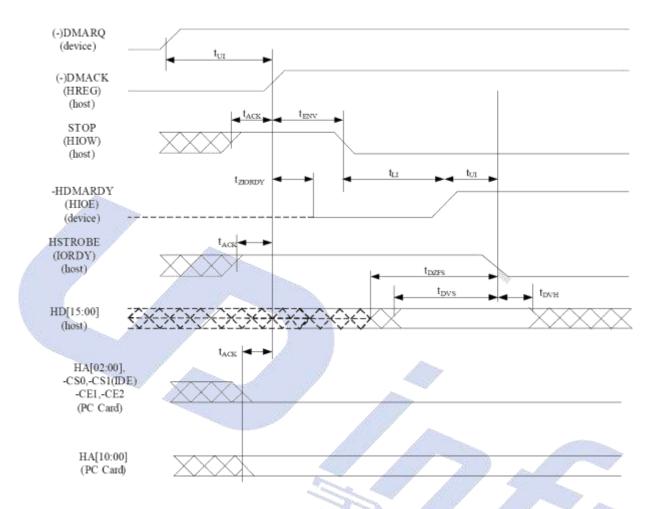

|     |        | 6.3.9.     | Ultra DMA Signal Usage In Each Interface Mode           | 33  |

|     |        | 6.3.10.    | Ultra DMA Data Burst Timing Requirements                | 30  |

|     |        | 6.3.11.    | Ultra DMA Data Burst Timing Descriptions                | 32  |

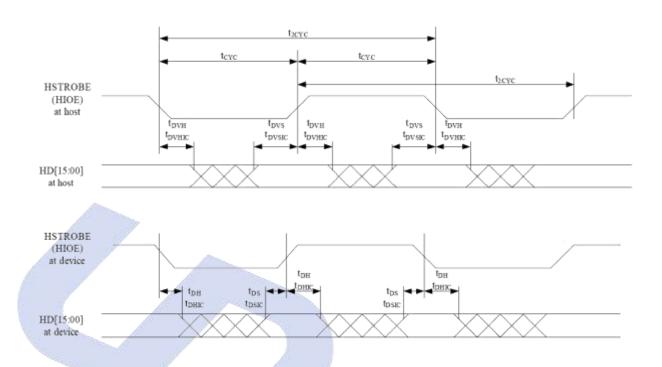

|    | 6.3.12.     | Ultra DMA Sender and Recipient IC Timing Requirements | 34 |

|----|-------------|-------------------------------------------------------|----|

|    | 6.3.13.     | Ultra DMA AC Signal Requirements                      | 35 |

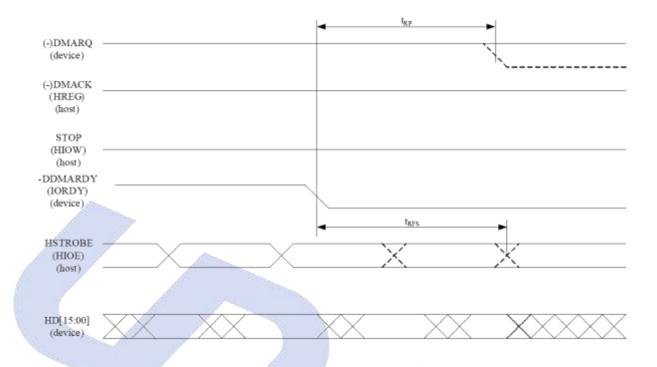

|    | 6.3.14.     | Ultra DMA Data-In Burst Initiation Timing             | 36 |

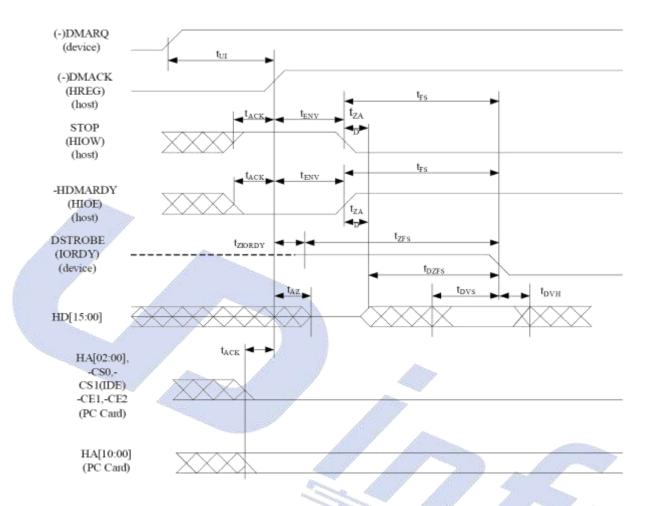

|    | 6.3.15.     | Sustained Ultra DMA Data-In Burst Timing              | 37 |

|    | 6.3.16.     | Ultra DMA Data-In Burst Host Pause Timing             | 38 |

|    | 6.3.17.     | Ultra DMA Data-In Burst Device Termination Timing     | 39 |

|    | 6.3.18.     | Ultra DMA Data-In Burst Host Termination Timing       | 40 |

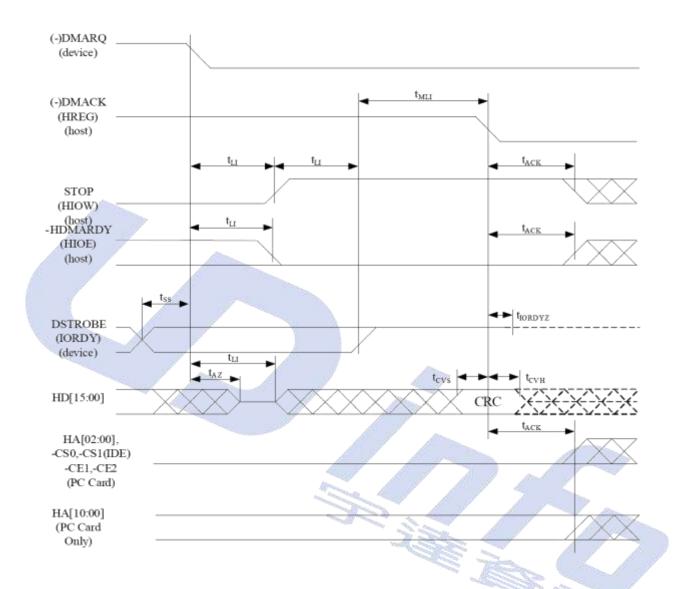

|    | 6.3.19.     | Ultra DMA Data-Out Burst Initiation Timing            | 41 |

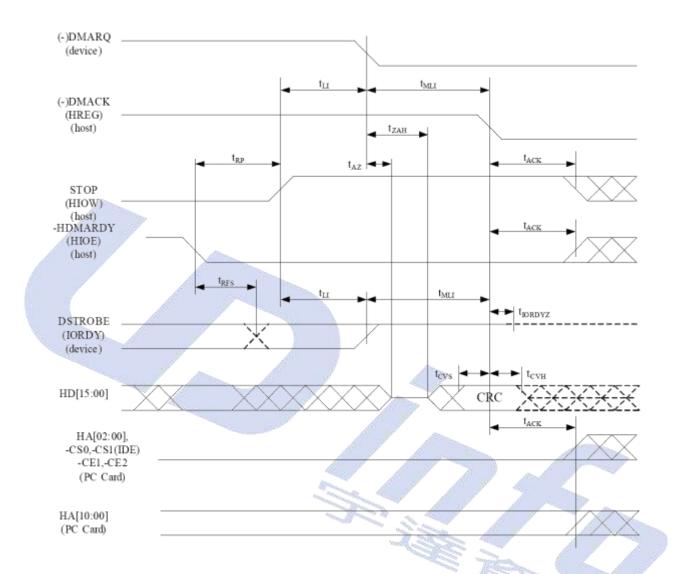

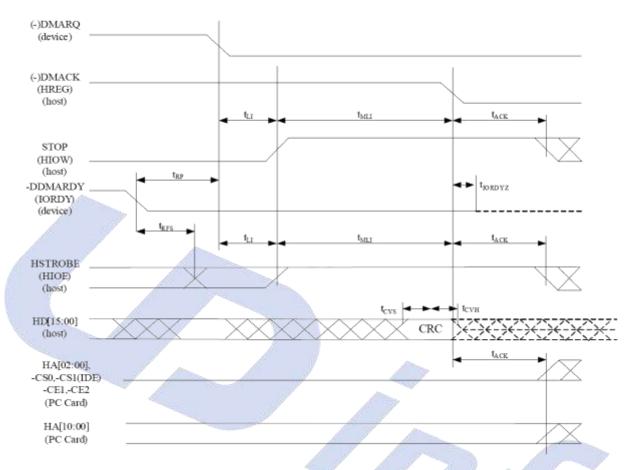

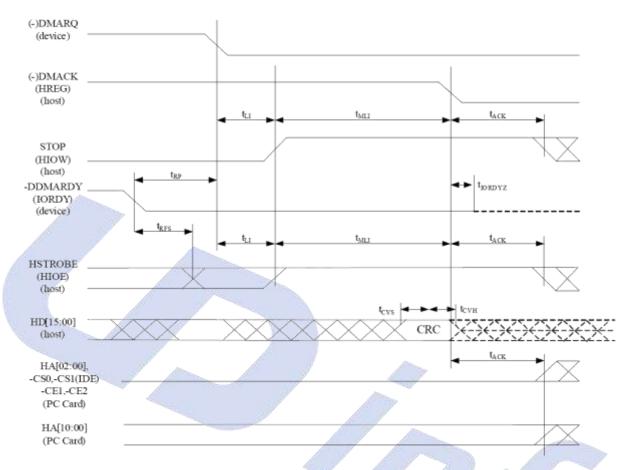

|    | 6.3.20.     | Sustained Ultra DMA Data-Out Burst Timing             | 42 |

|    | 6.3.21.     | Ultra DMA Data-Out Burst Device Pause Timing          | 43 |

|    | 6.3.22.     | Ultra DMA Data-Out Burst Device Termination Timing    | 44 |

|    | 6.3.23.     | Ultra DMA Data-Out Burst Host Termination Timing      | 45 |

| 5. | ATA Comman  | d Description                                         | 45 |

|    | 7.1. ATA C  | ommand Set                                            | 47 |

|    | 7.2. SMAR   | T Command Support                                     | 48 |

|    | 7.3. Identi | fy Drive Information(True IDE Mode)                   | 50 |

|    | 7.4. ID Tab | ole Information (PCMCIA Mode)                         | 52 |

| 6. | Part number | decoder                                               | 61 |

#### 1. Scope

This document describes the features and specifications and installation guide of AFAYA's *PCMCIA-ATA FLASH CARD* Products.

#### 2. Introduction

The PCMCIA-ATA FLASH CARD is solid-state design and IDE compatible.

It is an ideal replacement for standard IDE hard disks.

It's a solid-state design offers no seek errors even under extreme shock and vibration conditions. The *PCMCIA-ATA FLASH CARD* is extremely small and highly suitable for rugged environments, thus providing an excellent solution for mobile applications with space limitations. It is fully compatible with all consumer applications designed for data storage PC card, PDA, and Smart Cellular Phones, allowing simple use for the end user. The *PCMCIA-ATA FLASH CARD* is O/S independent, thus offering an optimal solution for embedded systems operating in non-standard computing environments. The *PCMCIA-ATA FLASH CARD* is IDE compatible and offering various capacities. It has low power consumption and can operate from a single 3.3/5.0 Volt power supply. The *PCMCIA-ATA FLASH CARD* provides memory storage for mobile computing applications, consumer electronics and embedded systems. It is fully compatible with existing systems.

#### 3. System Features

- Operating Modes:

- PC Card Memory Mode.

- PC Card I/O Mode.

- True-IDE Mode.

- Host Interface Supports

- Multi-Word DMA Modes 0~4

- Ultra DMA Modes 0~6

- PCMCIA Extended Memory Mode Cycle time: 250, 120, 100, 80ns

- PCMCIA Ultra DMA Modes 0~6

- Hardware RS-code ECC capable of correcting 24 bits in a 1,024 byte data

- Reliable Wear-leveling algorithm to ensure the best of flash endurance.

- Very low power consumption

- Very high performance

- Rugged environment is working well

- Automatic error correction and retry capabilities

- Supports power down commands and Auto Stand-by / Sleep Mode

- +5 V  $\pm 10\%$  or +3.3 V  $\pm 5\%$  operation

- MTBF > 2,000,000 hours

- Capacity: 128MB, 256MB, 512 MB, 1GB, 2GB, 4GB, 8GB, 16GB, 32GB(unformatted)

#### 4. Product Specifications

For all the following specifications, values are defined at ambient temperature and nominal supply voltage unless otherwise stated.

#### 4.1. System Environmental Specification

| Re            | ferral Part Number | ATA68SIXXXX <sup>1</sup> BX <sup>2</sup> X <sup>3</sup> X <sup>4</sup> |  |  |

|---------------|--------------------|------------------------------------------------------------------------|--|--|

| Standard      | Operating          | 0ºC ~ +70ºC                                                            |  |  |

| Temperature   | Non-operating      | -20ºC ~ +80ºC                                                          |  |  |

| Wide          | Operating          | -40ºC ~ +85ºC                                                          |  |  |

| Temperature   | Non-operating      | -50ºC ~ +95ºC                                                          |  |  |

| 11            | Operating          | F9/ × QF9/ non condensing                                              |  |  |

| Humidity      | Non-operating      | 5% ~ 95% non-condensing                                                |  |  |

| Vibration     | Operating          | 1FC mosk to mosk maximum                                               |  |  |

| Vibration     | Non-operating      | 15G peak-to-peak maximum                                               |  |  |

| Charle        | Operating          | 2000 C mavimum                                                         |  |  |

| Shock         | Non-operating      | 2000 G maximum                                                         |  |  |

| A latin all a | Operating          | E0 000 fact maximum                                                    |  |  |

| Altitude      | Non-operating      | 50,000 feet maximum                                                    |  |  |

#### Note:

- 1) XXXX<sup>1</sup>: Capacity, include 128MB ,256M, 512M, 001G, 002G, 004G, 008G ,016GB and 032G

- 2) X<sup>2</sup>:Temperature Grade I: (Wide temperature) C: (Standard temperature)

- 3) X1: Disk mode, include F:(Fixed Disk Mode), R: (Removable Disk Mode) and, A: Auto Detect Disk Mode

- 4) X<sup>4</sup>:Transfer mode, include P:(PIO mode), M:(Multi-Word Mode) and, U:(UDMA mode)

#### 4.2. System Power Requirement

| Referral Par          | t Number             | ATA68SIXXXX <sup>1</sup> BX <sup>2</sup> X <sup>3</sup> X <sup>4</sup> |

|-----------------------|----------------------|------------------------------------------------------------------------|

| DC Input Voltage 100n | nV max. ripple (p-p) | 5V±10%                                                                 |

| +5V Current           | Standby Mode:        | 12mA                                                                   |

| (Maximum average      | Reading Mode:        | 95mA                                                                   |

| value)                | Writing Mode:        | 140mA                                                                  |

#### Note:

- 1) XXXX<sup>1</sup>: Capacity, include 128MB ,256M, 512M, 001G, 002G, 004G, 008G ,016GB and 032G

- 2) X<sup>2</sup>:Temperature Grade 1: (Wide temperature) C: (Standard temperature)

- 3) X¹: Disk mode, include F:(Fixed Disk Mode) ,R: (Removable Disk Mode) and, A: Auto Detect Disk Mode

- 4) X<sup>4</sup>:Transfer mode, include P:(PIO mode),M:(Multi-Word Mode) and, U:(UDMA mode)

#### 4.3. System Performance

| SLC Performance   | Sequential Read  | 43 M bytes / sec Max.   |  |  |

|-------------------|------------------|-------------------------|--|--|

| SEC PERIORITATIVE | Sequential Write | 35 M bytes / sec Max.   |  |  |

| MIC Dayfayyaaaa   | Sequential Read  | 35 M bytes / sec Max.   |  |  |

| MLC Performance   | Sequential Write | 15.5 M bytes / sec Max. |  |  |

### 4.4. System Reliability

| MTBF                     | > 2,000,000 hours                                                                                                 |

|--------------------------|-------------------------------------------------------------------------------------------------------------------|

| Data Reliability         | < 1 non-recoverable error in 10 <sup>14</sup> bits read<br>< 1 erroneous correction in 10 <sup>20</sup> bits read |

| Wear-leveling Algorithms | Supportive                                                                                                        |

| ECC Technology           | Hardware RS-code ECC capable of correcting 24 bits in a 1,024 byte data                                           |

| Endurance (SLC)          | Greater than 1,000,000 cycles Logically contributed by Wear-leveling and advanced bad sector management           |

| Endurance (MLC)          | Greater than 100,000 cycles Logically contributed by Wear-leveling and advanced bad sector management             |

| Data Retention           | 10 years                                                                                                          |

#### 4.5. Physical Characteristics

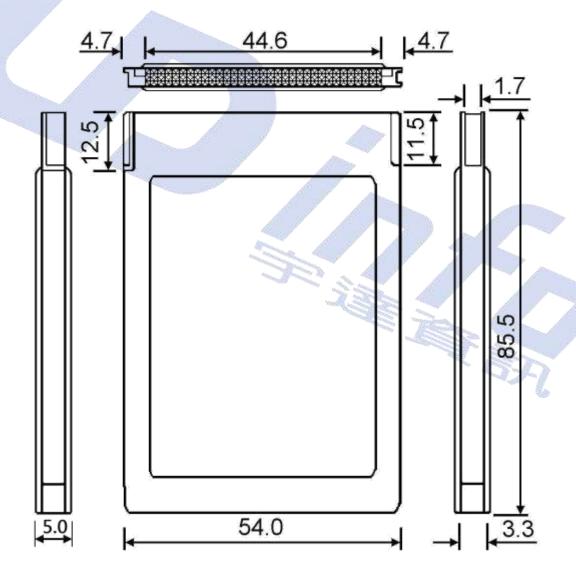

#### 4.5.1. Physical Specifications

| PCMCIA-ATA Flash Card            |  |  |  |  |  |  |

|----------------------------------|--|--|--|--|--|--|

| Length: 85.5 ± 0.1 mm            |  |  |  |  |  |  |

| Width: 54.4 ± 0.1 mm             |  |  |  |  |  |  |

| Thickness: 5.0 ± 0.1 mm          |  |  |  |  |  |  |

| Weight: 28.6 g (1.00 oz) maximum |  |  |  |  |  |  |

#### 4.5.2. PCMCIA-ATA Flash Card Dimension

#### 4.6. Capacity Specification

The specific capacities for the various models and the default number of heads, sectors and cylinders.

| Capacity | Default Cylinder | Default Head | Default Sector | User Data Size   |

|----------|------------------|--------------|----------------|------------------|

| 128MB    | 243              | 16           | 63             |                  |

| 256MB    | 487              | 16           | 63             |                  |

| 512MB    | 991              | 16           | 63             |                  |

| 1GB      | 1,966            | 16           | 63             | Depended on file |

| 2GB      | 3,900            | 16           | 63             | Depended on file |

| 4GB      | 7,785            | 16           | 63             | management       |

| 8GB      | 15,538           | 16           | 63             |                  |

| 16GB     | 31,045           | 16           | 63             |                  |

| 32GB     | 62,041           | 16           | 63             |                  |

#### 4.7. Card Block Diagram

### **5.** Interface Description

### 5.1. Pin Assignments

| PC Card Memory Mode |          |                                         | PC Card I/O Mode |        |        | True IDE Mode |                  |        |

|---------------------|----------|-----------------------------------------|------------------|--------|--------|---------------|------------------|--------|

| Pin                 | Signal   | Pin                                     | Pin              | Signal | Pin    | Pin           | Signal           | Pin    |

| No.                 | Name     | Туре                                    | No.              | Name   | Туре   | No.           | Name             | Туре   |

| 1                   | GND      | Ground                                  | 1                | GND    | Ground | 1             | GND              | Ground |

| 2                   | D3       | 1/0                                     | 2                | D3     | I/O    | 2             | D3               | I/O    |

| 3                   | D4       | 1/0                                     | 3                | D4     | I/O    | 3             | D4               | I/O    |

| 4                   | D5       | 1/0                                     | 4                | D5     | I/O    | 4             | D5               | I/O    |

| 5                   | D6       | I/O                                     | 5                | D6     | I/O    | 5             | D6               | I/O    |

| 6                   | D7       | I/O                                     | 6                | D7     | I/O    | 6             | D7               | I/O    |

| 7                   | CE1#     | 1                                       | 7                | CE1#   | 1      | 7             | CS0#             | 1      |

| 8                   | A10      | L/                                      | 8                | A10    | 1      | 8             | A10 <sup>2</sup> | 1      |

| 9                   | OE#      | 1                                       | 9                | OE#    | 1      | 9             | OE#              | 1      |

| 10                  | NC       | - ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 10               | NC     | -      | 10            | NC               | -      |

| 11                  | A9       | T                                       | 11               | A9     | 1      | 11            | A9 <sup>2</sup>  | 1      |

| 12                  | A8       | I                                       | 12               | A8     | ı 🤚    | 12            | A8 <sup>2</sup>  | 1      |

| 13                  | NC       | 4                                       | 13               | NC     |        | 13            | NC               | -      |

| 14                  | NC       | -                                       | 14               | NC     | 4      | 14            | NC               | -      |

| 15                  | WE#      | 1                                       | 15               | WE#    | 1      | 15            | WE# <sup>3</sup> |        |

| 16                  | RDY/BSY# | 0                                       | 16               | IREQ#  | 0      | 16            | INTRQ            | 0      |

| 17                  | VCC      | Power                                   | 17               | VCC    | Power  | 17            | VCC              | Power  |

| 18                  | NC       | -                                       | 18               | NC     | - 33   | 18            | NC               | - / /2 |

| 19                  | NC       | -                                       | 19               | NC     | -      | 19            | NC               | EZ.    |

| 20                  | NC       | -                                       | 20               | NC     | -      | 20            | NC               |        |

| 21                  | NC       | -                                       | 21               | NC     | -      | 21            | NC A             | 3-15   |

| 22                  | A7       | I                                       | 22               | A7     | 1      | 22            | A7 <sup>2</sup>  | 1 6    |

| 23                  | A6       | I                                       | 23               | A6     | 1      | 23            | A6 <sup>2</sup>  | I      |

| 24                  | A5       | 1                                       | 24               | A5     | 1      | 24            | A5 <sup>2</sup>  | 1      |

| 25                  | A4       | 1                                       | 25               | A4     | 1      | 25            | A4 <sup>2</sup>  | 1      |

| 26                  | A3       | 1                                       | 26               | A3     | 1      | 26            | A3 <sup>2</sup>  | 1      |

| 27                  | A2       | I                                       | 27               | A2     | 1      | 27            | A2               | 1      |

| 28                  | A1       | 1                                       | 28               | A1     | 1      | 28            | A1               | 1      |

| 29                  | A0       | 1                                       | 29               | A0     | 1      | 29            | A0               | 1      |

| 30                  | D0       | 1/0                                     | 30               | D0     | I/O    | 30            | D0               | 1/0    |

| 31                  | D1       | 1/0                                     | 31               | D1     | I/O    | 31            | D1               | I/O    |

| 32  | D2                | I/O     | 32  | D2               | I/O    | 32  | D2                | I/O    |

|-----|-------------------|---------|-----|------------------|--------|-----|-------------------|--------|

| 33  | WP                | 0       | 33  | IOIS16#          | 0      | 33  | IOCS16#           | 0      |

| 34  | GND               | Ground  | 34  | GND              | Ground | 34  | GND               | Ground |

| 35  | GND               | Ground  | 35  | GND              | Ground | 35  | GND               | Ground |

| Pin | Signal            | Pin     | Pin | Signal           | Pin    | Pin | Signal            | Pin    |

| No. | Name              | Туре    | No. | Name             | Туре   | No. | Name              | Туре   |

| 36  | CD1#              | 0       | 36  | CD1#             | 0      | 36  | CD1#              | 0      |

| 37  | D11 <sup>1</sup>  | 1/0     | 37  | D11 <sup>1</sup> | 1/0    | 37  | D11 <sup>1</sup>  | I/O    |

| 38  | D12 <sup>1</sup>  | 1/0     | 38  | D12 <sup>1</sup> | I/O    | 38  | D12 <sup>1</sup>  | I/O    |

| 39  | D13 <sup>1</sup>  | 1/0     | 39  | D13 <sup>1</sup> | 1/0    | 39  | D13 <sup>1</sup>  | I/O    |

| 40  | D14 <sup>1</sup>  | 1/0     | 40  | D14 <sup>1</sup> | I/O    | 40  | D14 <sup>1</sup>  | I/O    |

| 41  | D15 <sup>1</sup>  | 1/0     | 41  | D15 <sup>1</sup> | 1/0    | 41  | D15 <sup>1</sup>  | I/O    |

| 42  | CE2# <sup>1</sup> | 1       | 42  | CE2#1            | _      | 42  | CS1# <sup>1</sup> | I      |

| 43  | VS1#              | 0       | 43  | VS1#             | 0      | 43  | VS1#              | 0      |

| 44  | IORD#             | 1       | 44  | IORD#            | _      | 44  | IORD              | I      |

| 45  | IOWR#             | I, harm | 45  | IOWR#            | 1      | 45  | IOWR              | I      |

| 46  | NC                | -       | 46  | NC               | -      | 46  | NC                | -      |

| 47  | NC .              |         | 47  | NC               | -      | 47  | NC                | -      |

| 48  | NC                | -       | 48  | NC               | £.     | 48  | NC                | -      |

| 49  | NC                | -       | 49  | NC               |        | 49  | NC                | -      |

| 50  | NC                | -       | 50  | NC 🥠             | - 4    | 50  | NC                | -      |

| 51  | VCC               | Power   | 51  | VCC              | Power  | 51  | vcc               | Power  |

| 52  | NC                | -       | 52  | NC S             | 3 3    | 52  | VPP               | -      |

| 53  | NC                | -       | 53  | NC               | - 43   | 53  | NC                | -//    |

| 54  | NC                | -       | 54  | NC               | -      | 54  | NC                | -      |

| 55  | NC                | -       | 55  | NC               | -      | 55  | NC                | -      |

| 56  | NC                | -       | 56  | NC               | -      | 56  | CSEL#             | 17-1   |

| 57  | VS2#              | 0       | 57  | VS2#             | 0      | 57  | VS2#              | 0      |

| 58  | RESET             | 1       | 58  | RESET            | 1      | 58  | RESET#            | I      |

| 59  | WAIT#             | 0       | 59  | WAIT#            | 0      | 59  | IORDY             | 0      |

| 60  | INPACK#           | 0       | 60  | INPACK#          | 0      | 60  | DREQ              | 0      |

| 61  | REG#              | 1       | 61  | REG#             | 1      | 61  | DMACK             | I      |

| 62  | BVD2              | 1/0     | 62  | SPKR#            | I/O    | 62  | DASP#             | 1/0    |

| 63  | BVD1              | 1/0     | 63  | STSCHG#          | I/O    | 63  | PDIAG#            | 1/0    |

| 64  | D8 <sup>1</sup>   | 1/0     | 64  | D8 <sup>1</sup>  | 1/0    | 64  | D8 <sup>1</sup>   | 1/0    |

| 65  | D9 <sup>1</sup>   | 1/0     | 65  | D9 <sup>1</sup>  | I/O    | 65  | D9 <sup>1</sup>   | I/O    |

| 66 | D10 <sup>1</sup> | 1/0    | 66 | D10 <sup>1</sup> | 1/0    | 66 | D10 <sup>1</sup> | I/O    |

|----|------------------|--------|----|------------------|--------|----|------------------|--------|

| 67 | CD2#             | 0      | 67 | CD2#             | 0      | 67 | CD2#             | 0      |

| 68 | GND              | Ground | 68 | GND              | Ground | 68 | GND              | Ground |

#### Note:

- 1) 1. Signals marked with an asterisk are required for 16-bit access, not required when installed in 8-bit systems.

- 2) 2. Should be grounded by the host.

#### **5.2.** Pin Descriptions

| Signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Mode of predation   | Pin Type   Pin |                                         | Description                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------|-----------------------------------------|--------------------------------------------------|

| Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     | No(s).         |                                         |                                                  |

| CD1#,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     | 0 36, 67       |                                         | Card Detect Outputs                              |

| CD2#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PC Card Memory Mode |                | These Card Detect pins are connected to |                                                  |

| \                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                     |                |                                         | ground on the PC Card. They are used by the      |

| A STATE OF THE STA |                     |                |                                         | host to determine that the PC Card is fully      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |                | y                                       | inserted into the socket.                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PC Card I/O Mode    |                | 7                                       | This signal is same in this mode.                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | True IDE Mode       |                |                                         | This signal is same in this mode.                |

| IOWR#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     | I              | 45                                      | I/O Write Input                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PC Card Memory Mode |                |                                         | This signal is not used in this mode.            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PC Card I/O Mode    |                |                                         | The I/O Write strobe pulse is used to clock I/O  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |                |                                         | data on the Card Data bus into the PC Card       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |                |                                         | controller registers. The clocking will occur on |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |                |                                         | the negative to positive going edge of the       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |                |                                         | signal.                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | True IDE Mode       |                |                                         | This signal has the same function as in PC       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |                |                                         | Card I/O Mode.                                   |

| IORD#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     | 1              | 44                                      | I/O Read Input                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PC Card Memory Mode |                |                                         | This signal is not used in this mode.            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PC Card I/O Mode    |                |                                         | This is an I/O Read strobe generated by the      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |                |                                         | host. This signal gates I/O data onto the bus    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |                |                                         | from the PC Card.                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | True IDE Mode       |                |                                         | This signal has the same function as in PC       |